Treten Sie dem Forum für Designer bei!

Ihr Fachwissen ist wichtig für die Gemeinschaft. Helfen Sie uns und bringen Sie Ihr Wissen ein!

Jetzt dem Forum beitretenTauschen Sie sich aus, lernen Sie und wachsen Sie mit den besten Fachleuten der Branche.

Warum HFSS-IC?

Ansys hat mit HFSS-IC ein neues Tool für kleine und mittlere Unternehmen herausgebracht. Es ermöglicht den Entwurf komplexer, auf Gehäusen montierter und in Leiterplatten integrierter Die-Baugruppen. Die Lösung umfasst drei robuste Solver – HFSS, Q3D und RaptorX – und bietet im Vergleich zu anderen Marktalternativen eine breite Palette von Funktionen:

- Kann GDS-Dateien und unterstützende Dateien (*.map oder *.xml) lesen.

- Kann Foundry-verschlüsselte Modelle lesen. Zugelassen von der Hauptgießerei.

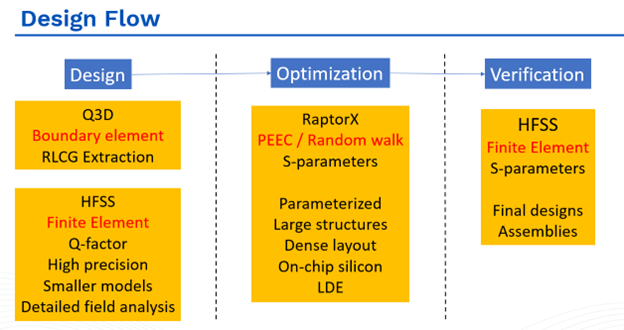

- 3 Solver (HFSS/Q3D/RaptorX) für vollständige Entwurfsmöglichkeiten in allen Entwurfsstadien.

- HFSS ist der Industriestandard für die Lösung elektromagnetischer Probleme

- Die meisten Gießereien genehmigen RaptorX.

- Unterstützt komplizierte Die(s)-auf-Die-auf-Package-Konfigurationen.

- Innovative Werkzeuge zur Vereinfachung des Modells und der Vernetzung.

- Parametrisierung für die drei Solver, mit intelligentem Optimierer unter Verwendung von Optislang.

- Verbunden mit dem AEDT-Kreislauf, 2-Wege-Verbindung.

- Erschwinglicher Preis für kleine und mittlere Unternehmen.

GDS-Dateien:

Das GDS-Dateiformat ist das am häufigsten verwendete Format in der Chip-Industrie. Die HFSS-IC-Lösung ist in der Lage, GDS-Dateien sowie Stackup-Dateien wie .map, .xml und *.ircx, unter anderem, zu lesen. Wählen Sie im Hauptmenü File>Import>GDS files:

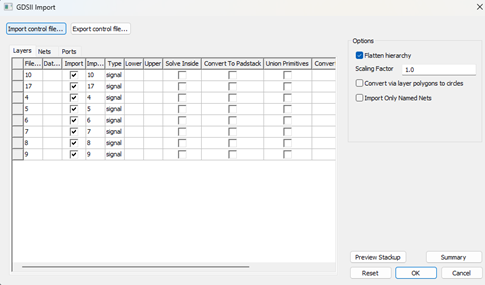

Nach der Auswahl der GDS-Datei zeigt AEDT die Liste der Ebenen, eine Liste der Netze und der Anschlüsse an. Es bietet dem Benutzer auch die Möglichkeit, Kontrolldateien zu importieren:

Sie können die folgenden Dateitypen zur Steuerung/Unterstützung hochladen: *.xml, *.tech, *.layermap, *.ircx, *.itf,* .vlc.tech, und *.map Dateien.

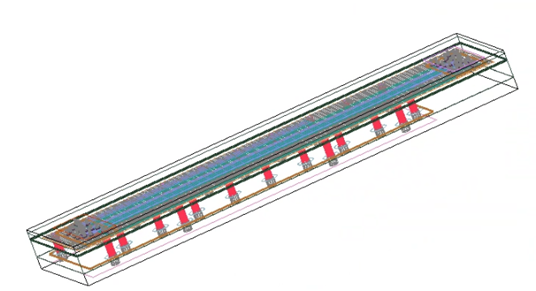

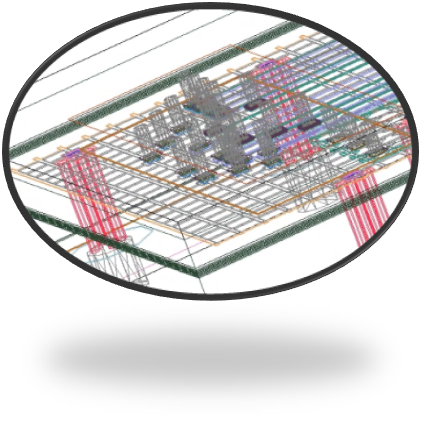

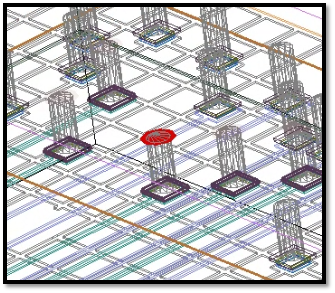

Das für diesen Blog verwendete Beispiel ist ein Silizium-Interposer:

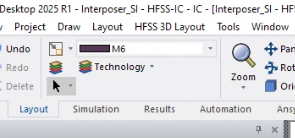

HFSS/3D Layout Standardmodus und HFSS-IC-Modus.

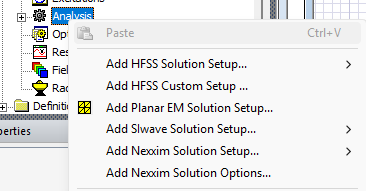

Im HFSS/3D-Layout-Standardmodus hat der Benutzer Zugriff auf HFSS-, Planar- und SIwave-DICR/PI-Solver.

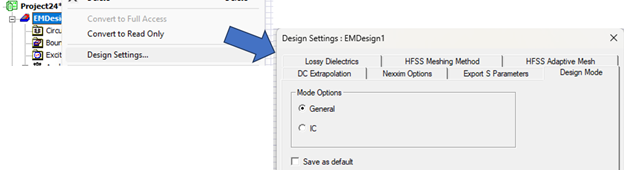

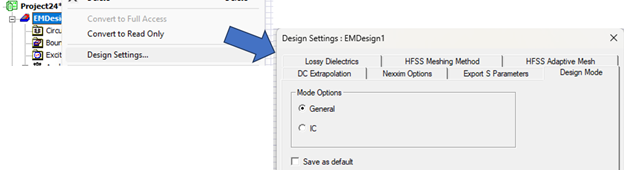

Der Benutzer kann in den HFSS-IC-Modus wechseln, indem er mit der rechten Maustaste auf den Namen des Modells>Design Settings> Design Mode klickt.

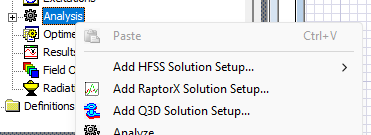

Durch Umschalten in den IC-Modus erhält der Benutzer Zugriff auf die drei Solver: HFSS, Q3D und RaptorX.

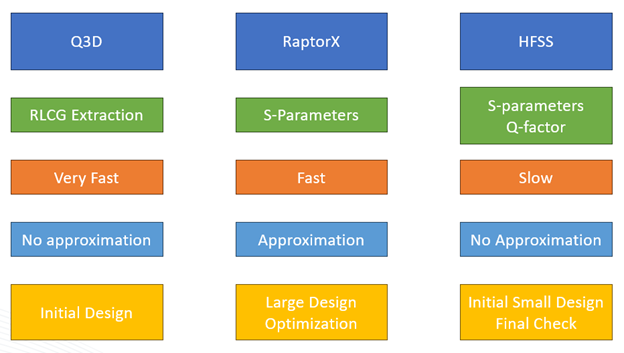

In der folgenden Tabelle sind die wichtigsten Merkmale der einzelnen Typen zusammengefasst:

Wann sollte man welchen Solver verwenden? Jeder Solver hat seine eigenen Fähigkeiten und Stärken. Der Benutzer muss für jede Phase das richtige Werkzeug auswählen. Diese Werkzeuge sind alles, was der Benutzer für einen schnellen und reibungslosen Entwurf tun muss.

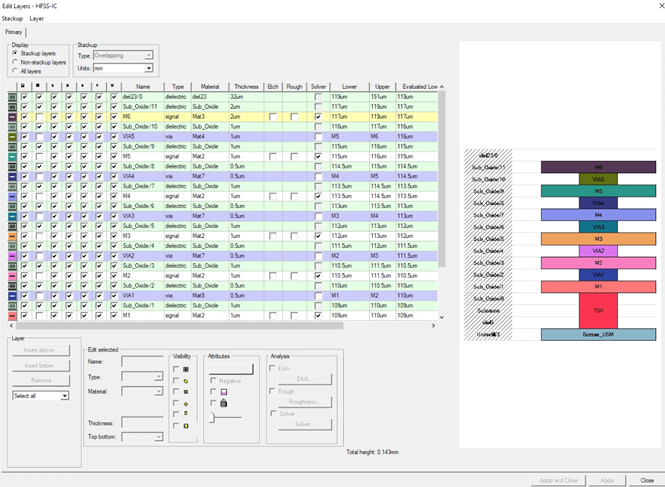

IC-Modus Stackup

Als erstes muss der Stackup im Modell überprüft werden. Wählen Sie das Stackup-Symbol:

Stapelungen im IC-Modus sind immer überlappende Stapelungen. In diesem Modus ist es möglich, verschiedene Ebenen zu überlappen. Der Benutzer muss lediglich die unteren und oberen Abmessungen der einzelnen Schichten angeben. Neben der Änderung von Schichten und Materialien kann der Benutzer auch Effekte wie Ätzen und Oberflächenrauhigkeit hinzufügen. Im IC-Modus gibt es auch VIA-Schichten. Die unteren und oberen Abmessungen der Via-Lagen werden mit dem Namen der Metall-Lage angegeben, z. B. M5, M6, usw.

![]()

IC-Modus Ports

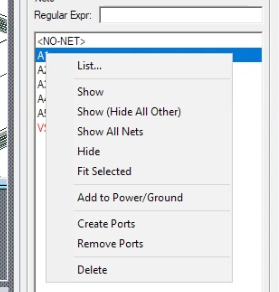

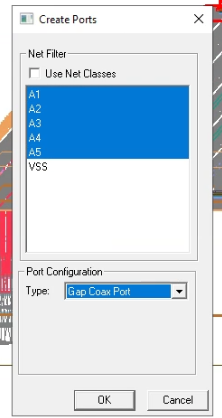

In HFSS können Benutzer Ports auf verschiedene Weise hinzufügen. Die drei Solver akzeptieren alle Typen. Die erste Möglichkeit zum Hinzufügen von Anschlüssen besteht darin, ein Netzwerk auszuwählen und dann mit der rechten Maustaste zu klicken, um Anschlüsse an beiden Enden des Netzwerks hinzuzufügen.

Die andere Möglichkeit ist, eine Komponente auszuwählen und dann mit der rechten Maustaste zu klicken, um Anschlüsse hinzuzufügen:

Auf diese beiden Arten entsteht ein Anschluss mit koaxialem Spalt.

Modell-Bearbeitung

Es wird dringend empfohlen, RaptorX während der Entwurfsphase zu verwenden, insbesondere während der Optimierung. Um genauere Ergebnisse zu erhalten, muss der Benutzer auch in der Lage sein, HFSS zu verwenden. Der IC-Modus wurde mit intelligenten Werkzeugen ausgestattet, um Änderungen am Entwurf vorzunehmen und kleine Abmessungen zu eliminieren, wodurch eine übermäßig lange Laufzeit von HFSS verhindert wird.

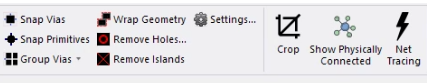

Bevor Sie jedoch eine dieser Funktionen nutzen können, müssen Sie die Einstellungen ändern. Klicken Sie auf die Schaltfläche „Einstellungen“:

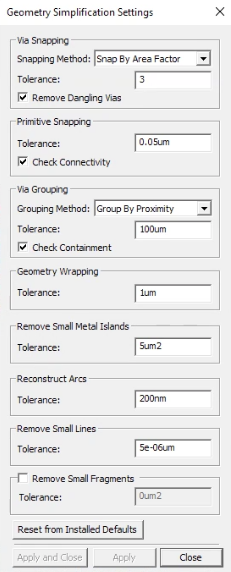

Um die Bedeutung der einzelnen Zahlen in den Einstellungen zu verstehen, gehen wir zurück zu den Werkzeugen:

- Vias fangen: Mit dieser Option wird der Querschnitt der Vias so verändert, dass er der Größe der Pads in der oberen oder unteren Schicht entspricht. Die Änderung erfolgt, wenn das Delta kleiner ist als das, was in den Kriterien für das Einrasten von Vias in der Einstellung angegeben ist.

- Primitive fangen: Mit dieser Option wird die Form der Netze in den Signallayern aneinander angeglichen. Die Änderung erfolgt, wenn das Delta kleiner ist, als in den Kriterien für das Einrasten von Primitiven in der Einstellung angegeben ist.

- Durchkontaktierungen gruppieren: Mit dieser Option werden Vias zu einem einzigen Netz gruppiert, wenn ihr Abstand geringer ist als in den Kriterien für die Via-Gruppierung in den Einstellungen angegeben.

- Geometrie umhüllen: Diese Option gruppiert Netze oder Vias zu einem einzigen Netz/einem einzigen Via und schließt Lücken, wenn die Lücken zwischen den Objekten kleiner sind als die Anzahl, die in den Geometrieumhüllungskriterien in den Einstellungen angegeben wurde.

- Löcher entfernen: Wenn das Netz in den Signallagen kleine Löcher mit einem Querschnitt aufweist, der kleiner ist als die in „Kleine Metallinseln entfernen“ angegebene Anzahl, wird es gefüllt.

- Inseln entfernen: Diese Option löscht einfach alle kleinen Inseln. Die Entscheidung basiert auf dem Kriterium Kleine Metallinseln entfernen in der Einstellung.

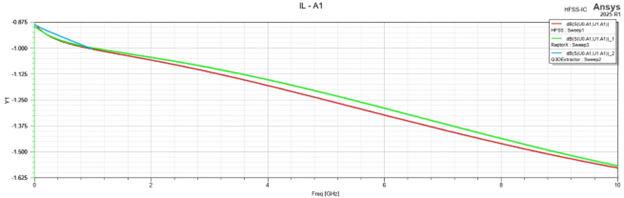

Unterschied zwischen den drei Solvern: Ergebnisse

Das folgende Diagramm zeigt den Unterschied zwischen den drei Solvern. Beachten Sie, dass wir Q3D für bis zu 1 GHz gelöst haben. Das ist alles, was wir brauchen, um das RLCG der Netze zu extrahieren.

Sowohl HFSS als auch RaptorX lieferten sehr ähnliche Ergebnisse. Das zeigt, dass der Benutzer RaptorX während des Optimierungsprozesses vertrauen kann. Die folgende Tabelle zeigt die Zeit, die jeder Solver für die Lösung benötigte. HFSS benötigte unter Verwendung der Standardeinstellungen 5 Mal länger als RaptorX. Diese Zeit kann verbessert werden, wenn der Benutzer ein intelligentes Meshing durchführt, indem er das Mesh in allen Objekten kontrolliert.

| Q3D (CG/DC RL/ AC RL) | RaptorX | HFSS (DC mit Q3D) | |

| Speicher | 7G | 12G | 126G |

| Simulation Zeit | 0:17 | 0:44 | 4:08 |

| Iterative Zeit | 0:12 (CG) | 0:57 | |

| Anzahl der Elemente | 0.106M Dreiecke (AC) 0,120 Mio. Salmler (DC) | 0.133M | 1.3M Mehrreihige Salmler |

Zusammenfassung

HFSS-IC ist eine robuste und budgetfreundliche Lösung, die für kleine bis mittlere Unternehmen entwickelt wurde. Sie integriert die vollen Fähigkeiten der Solver HFSS und RaptorX. Dieses Tool unterstützt den Entwurf einer breiten Palette von Konfigurationen, einschließlich Dies, gestapelten Dies, Dies auf Gehäusen und sogar komplexen, auf PCBs montierten Baugruppen – ohne Einschränkungen. Anwender können parasitäre Elemente extrahieren, Induktivitäten entwerfen, Übergänge und Leistungsteiler optimieren, Übersprechen abschwächen und vieles mehr.

Treten Sie dem Forum für Designer bei!

Ihr Fachwissen ist wichtig für die Gemeinschaft. Helfen Sie uns und bringen Sie Ihr Wissen ein!

Jetzt dem Forum beitretenTauschen Sie sich aus, lernen Sie und wachsen Sie mit den besten Fachleuten der Branche.