Rejoignez le forum des designers !

Votre expertise est essentielle pour la communauté. Rejoignez-nous et apportez vos connaissances !

Rejoindre le forum maintenantPartagez, apprenez et évoluez avec les meilleurs professionnels du secteur.

Pourquoi HFSS-IC ?

Ansys a lancé HFSS-IC, un nouvel outil destiné aux petites et moyennes entreprises. Il permet de concevoir des assemblages complexes de composants montés sur des boîtiers et intégrés sur des cartes de circuits imprimés. La solution comprend trois solveurs robustes – HFSS, Q3D et RaptorX – et offre un large éventail de fonctionnalités par rapport aux autres solutions disponibles sur le marché :

- Peut lire les fichiers GDS et les fichiers de support (*.map ou *.xml).

- Peut lire les modèles cryptés par la fonderie. Approuvé par la fonderie principale.

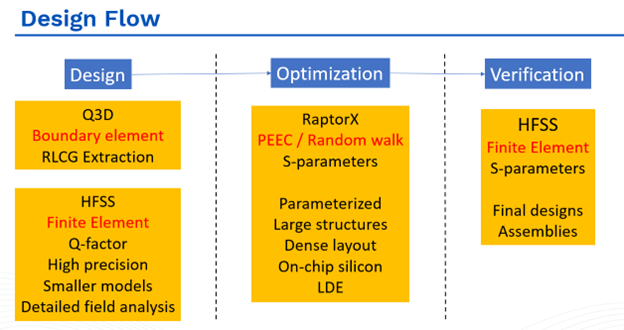

- 3 solveurs (HFSS/Q3D/RaptorX) pour des capacités de conception complètes à tous les stades de la conception.

- HFSS est la norme industrielle pour la résolution des problèmes électromagnétiques.

- La plupart des fonderies approuvent RaptorX.

- Prend en charge les configurations complexes « die(s) on-die-on-package ».

- Outils innovants pour simplifier le modèle et le maillage.

- Paramétrage des trois solveurs, avec optimiseur intelligent utilisant Optislang.

- Relié au circuit AEDT, connexion à deux voies.

- Prix abordable pour les petites et moyennes entreprises.

Fichiers GDS :

Le format de fichier GDS est le format le plus couramment utilisé dans l’industrie des matrices (puces). La solution HFSS-IC est capable de lire les fichiers GDS ainsi que les fichiers d’empilage tels que .map, .xml et *.ircx, entre autres. Dans le menu principal, sélectionnez File>Import>GDS files :

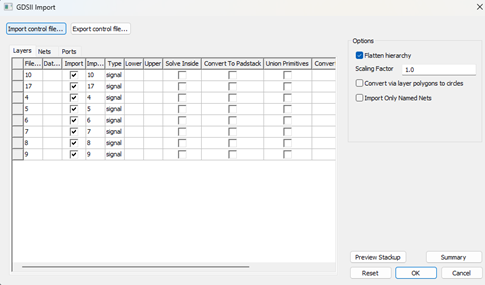

Après avoir sélectionné le fichier GDS, l’AEDT affiche la liste des couches, la liste des filets et des ports. Il permet également à l’utilisateur d’importer des fichiers de contrôle :

Vous pouvez télécharger les types de fichiers de contrôle/support suivants : *.xml, *.tech, *.layermap, *.ircx, *.itf,* .vlc.tech, et *.map.

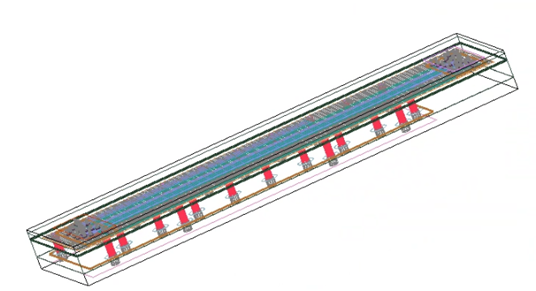

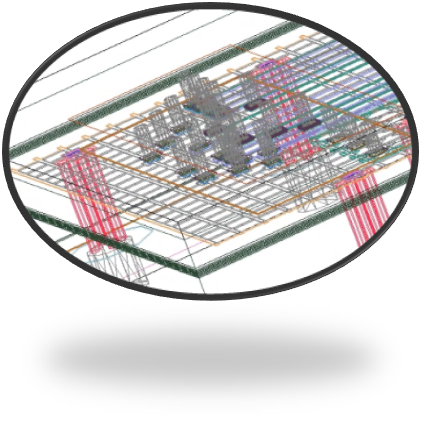

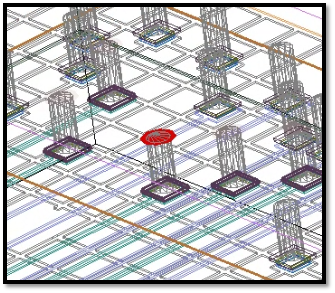

L’exemple utilisé pour ce blog est un interposeur de silicium :

Mode par défaut de HFSS/3D Layout et mode HFSS-IC.

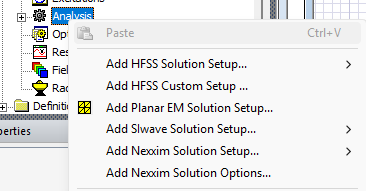

Dans le mode par défaut HFSS/3D Layout, l’utilisateur a accès aux solveurs HFSS, planaire et SIwave DICR/PI.

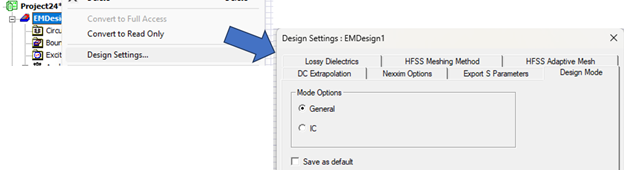

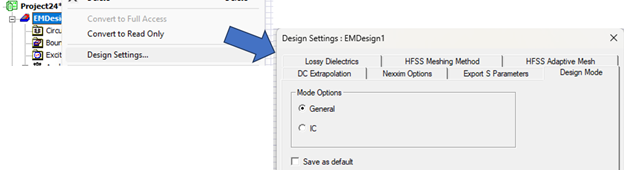

L’utilisateur peut passer au mode HFSS-IC en cliquant avec le bouton droit de la souris sur le nom du modèle>Design Settings> ; Design mode.

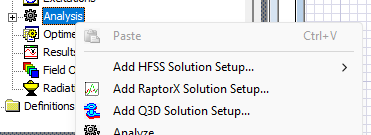

Le passage au mode IC permet à l’utilisateur d’accéder aux trois solveurs : HFSS, Q3D et RaptorX.

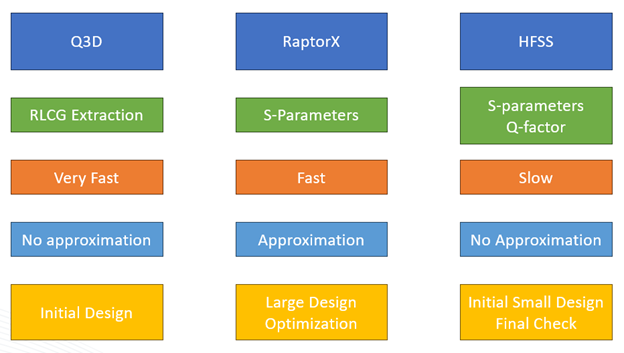

Le tableau suivant résume les principales caractéristiques de chaque type :

Quand utiliser chaque solution ? Chaque solveur a ses capacités et ses points forts. L’utilisateur doit choisir l’outil adéquat pour chaque étape. Ces outils sont tout ce dont l’utilisateur a besoin pour une conception rapide et fluide.

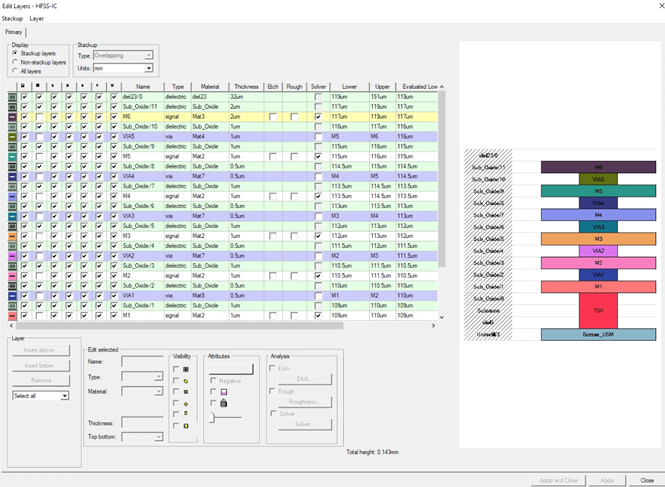

Mode IC Stackup

La première chose à vérifier est l’empilage dans le modèle. Sélectionnez l’icône de l’empilage :

Les empilages en mode IC sont toujours des empilages qui se chevauchent. Il est possible de superposer différentes couches dans ce mode. L’utilisateur doit simplement spécifier les dimensions inférieures et supérieures de chaque couche. Outre la modification des couches et des matériaux, l’utilisateur peut également ajouter des effets tels que la gravure et la rugosité de la surface. Le mode IC comprend également des couches VIA. Les dimensions inférieures et supérieures des couches Via sont spécifiées à l’aide du nom de la couche Métal, par exemple, M5, M6, etc.

![]()

Mode IC Ports

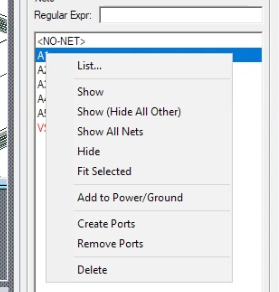

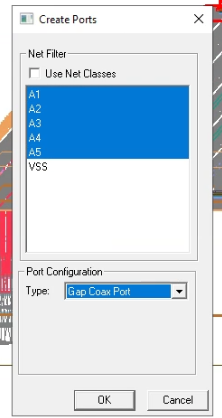

Dans HFSS, les utilisateurs peuvent ajouter des ports de différentes manières. Les trois solveurs acceptent tous les types. La première façon d’ajouter des ports consiste à sélectionner un réseau, puis à cliquer avec le bouton droit de la souris pour ajouter des ports aux deux extrémités du réseau.

L’autre méthode consiste à sélectionner un composant et à cliquer avec le bouton droit de la souris pour ajouter des ports :

Ces deux méthodes permettent de créer un port de type coaxial.

Modèles d’édition

Il est fortement recommandé d’utiliser RaptorX pendant la phase de conception, en particulier pendant l’optimisation. Pour obtenir des résultats plus précis, l’utilisateur doit également être en mesure d’utiliser HFSS. Le mode IC était équipé d’outils intelligents permettant d’apporter des modifications à la conception et d’éliminer les petites dimensions, ce qui empêchait le HFSS de fonctionner pendant une période excessivement longue.

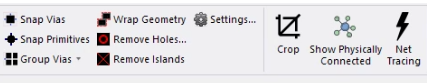

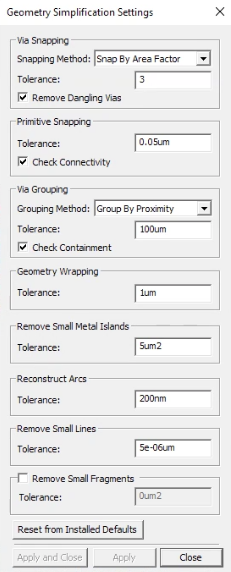

Cependant, avant d’utiliser l’un d’entre eux, l’utilisateur doit modifier les paramètres. Cliquez sur le bouton de réglage :

Pour comprendre la signification de chaque chiffre dans les paramètres, nous revenons aux outils :

- Snap vias : Cette option modifie la section transversale des vias pour qu’elle corresponde à la taille des pastilles de la couche supérieure ou inférieure. La modification a lieu si le delta est inférieur à ce qui est spécifié dans les critères d’accrochage des vias dans le paramètre.

- Snap Primitives : Cette option modifie la forme des réseaux dans les couches de signaux pour qu’ils correspondent les uns aux autres. Le changement se produit si le delta est inférieur à ce qui est spécifié dans les critères d’accrochage des primitives dans le paramètre.

- Group vias : Cette option regroupe les vias en un seul filet si leur espacement est inférieur à ce qui est spécifié dans les critères de regroupement des vias dans les paramètres.

- Wrap Geometry (Envelopper la géométrie) : Cette option regroupe les réseaux ou les vias en un seul réseau/un seul via et ferme les espaces si les espaces entre les objets sont inférieurs au nombre spécifié dans les critères d’enveloppement de la géométrie dans les paramètres.

- Supprimer les trous : Si le réseau dans les couches de signal a de petits trous avec une section transversale inférieure au nombre spécifié dans « Remove small metal islands », il sera rempli.

- Supprimer les îlots : Cette option supprime simplement tous les petits îlots. La décision est basée sur le critère Supprimer les petites îles métalliques dans le cadre.

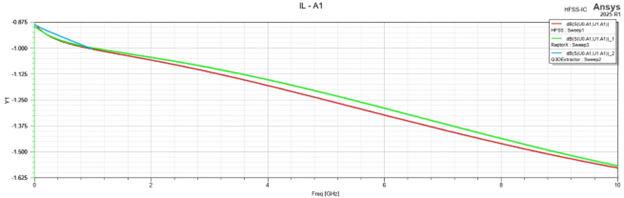

Différence entre les trois solveurs : Résultats

Le graphique suivant montre la différence entre les trois solveurs. Notez que nous avons résolu Q3D jusqu’à 1 GHz. C’est tout ce dont nous avons besoin pour extraire le RLCG des réseaux.

HFSS et RaptorX ont tous deux donné des résultats très proches. Cela indique que l’utilisateur peut faire confiance à RaptorX pendant le processus d’optimisation. Le tableau suivant montre le temps de résolution pour chaque solveur. HFSS, en utilisant la configuration par défaut, a pris 5 fois plus de temps que RaptorX. Ce temps peut être amélioré si l’utilisateur effectue un maillage intelligent en contrôlant le maillage dans tous les objets.

| Q3D (CG/DC RL/ AC RL) | RaptorX | HFSS (DC avec Q3D) | |

| Mémoire | 7G | 12G | 126G |

| Temps de simulation | 0:17 | 0:44 | 4:08 |

| Temps itératif | 0:12 (CG) | 0:57 | |

| Nombre d’éléments | 0.106M Triangles (AC) 0.120M Tetras (DC) | 0.133M | 1.3M Tétra aux ordres de Mult |

Résumé

HFSS-IC est une solution robuste et économique conçue pour les petites et moyennes entreprises. Il intègre toutes les capacités des solveurs HFSS et RaptorX. Cet outil prend en charge la conception d’un large éventail de configurations, y compris des matrices, des matrices empilées, des matrices sur des boîtiers et même des assemblages complexes montés sur des circuits imprimés, sans aucune limitation. Les utilisateurs peuvent extraire les éléments parasites, concevoir des inductances, optimiser les transitions et les diviseurs de puissance, atténuer la diaphonie, etc.

Rejoignez le forum des designers !

Votre expertise est essentielle pour la communauté. Rejoignez-nous et apportez vos connaissances !

Rejoindre le forum maintenantPartagez, apprenez et évoluez avec les meilleurs professionnels du secteur.