디자이너를 위한 포럼에 참여하기

여러분의 전문 지식은 커뮤니티에 매우 중요합니다. 참여하여 지식을 공유하세요

지금 포럼에 참여하세요업계 최고의 전문가들과 함께 공유하고 배우며 성장하세요.

왜 HFSS-IC인가?

Ansys는 중소기업을 위한 새로운 툴인 HFSS-IC를 출시했습니다. 이 툴을 사용하면 패키지에 장착되고 인쇄 회로 기판에 통합된 복잡한 다이 어셈블리를 설계할 수 있습니다. 이 솔루션에는 세 가지 강력한 솔버인 HFSS, Q3D 및 RaptorX가 포함되어 있으며 다른 시장의 대안과 비교하여 광범위한 기능을 제공합니다:

- GDS 파일 및 지원 파일(*.map 또는 *.xml)을 읽을 수 있습니다.

- 파운드리 암호화 모델을 읽을 수 있습니다. 메인 파운드리에서 승인했습니다.

- 모든 설계 단계에서 완벽한 설계 기능을 위한 3개의 솔버(HFSS/Q3D/RaptorX).

- HFSS는 전자기 문제 해결을 위한 업계 표준입니다.

- 대부분의 파운드리는 RaptorX를 승인합니다.

- 복잡한 다이 온 다이 온 패키지 구성을 지원합니다.

- 모델과 메시를 간소화하는 혁신적인 툴.

- Optislang을 사용한 스마트 옵티마이저로 세 가지 솔버에 대한 매개변수화.

- AEDT 회로에 연결, 양방향 연결.

- 중소기업을 위한 합리적인 가격.

GDS 파일:

GDS 파일 형식은 금형(칩) 업계에서 가장 일반적으로 사용되는 형식입니다. HFSS-IC 솔루션은 GDS 파일뿐만 아니라 .map, .xml, *.ircx와 같은 스택업 파일도 읽을 수 있습니다. 메인 메뉴의 파일에서 GDS 파일 가져오기를 선택합니다:

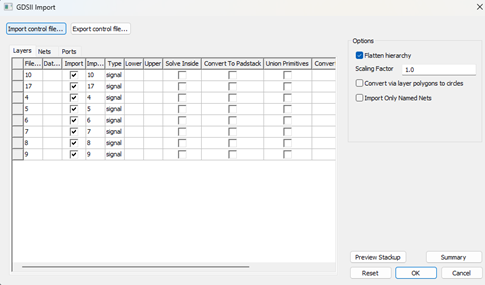

GDS 파일을 선택하면 AEDT는 레이어 목록, 네트 목록, 포트 목록을 표시합니다. 또한 사용자에게 제어 파일을 가져올 수 있는 기능도 제공합니다:

다음 제어/지원 파일 형식을 업로드할 수 있습니다: *.xml, *.tech, *.layermap, *.ircx, *.itf, *.vlc.tech 및 *.map 파일.

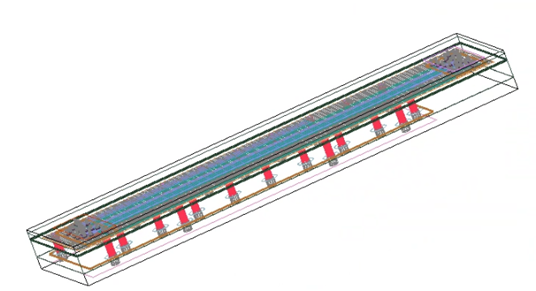

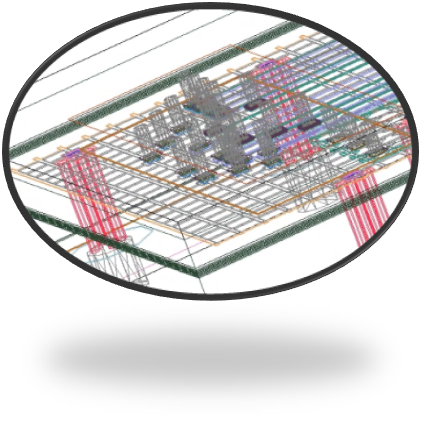

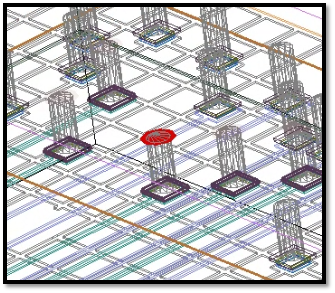

이 블로그에 사용된 예제는 실리콘 인터포저입니다:

HFSS/3D 레이아웃 기본 모드 및 HFSS-IC 모드.

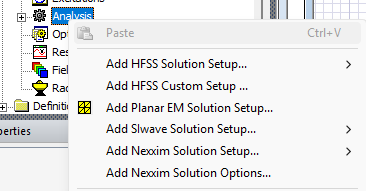

HFSS/3D 레이아웃 기본 모드에서 사용자는 HFSS, 평면형 및 SIwave DICR/PI 솔버에 액세스할 수 있습니다.

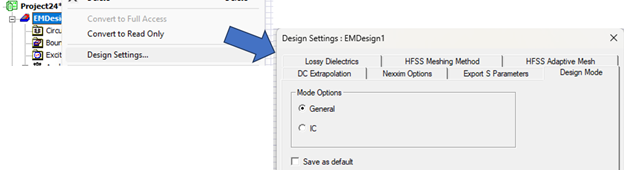

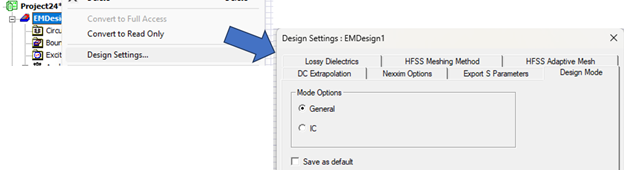

사용자는 모델명 <디자인 설정> <디자인 모드>를 마우스 오른쪽 버튼으로 클릭하여 HFSS-IC 모드로 전환할 수 있습니다.

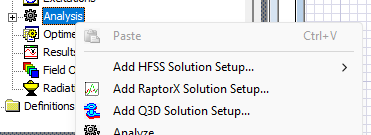

IC 모드로 전환하면 사용자는 세 가지 솔버에 액세스할 수 있습니다: HFSS, Q3D, RaptorX.

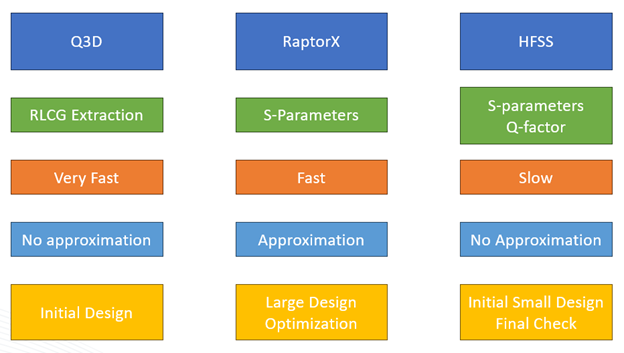

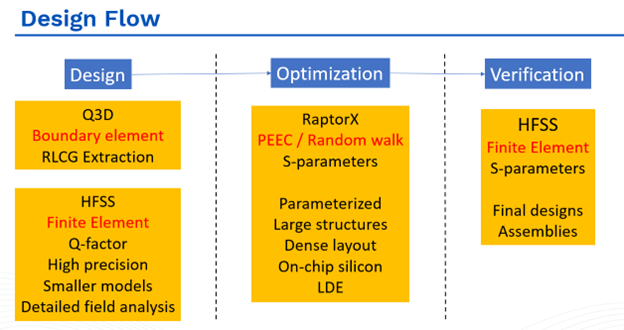

다음 표에는 각 유형의 주요 기능이 요약되어 있습니다:

각 솔버는 언제 사용하나요? 각 솔버마다 기능과 강점이 있습니다. 사용자는 각 단계에 적합한 툴을 선택해야 합니다. 이러한 도구는 빠르고 원활한 설계를 위해 사용자가 필요한 모든 것입니다.

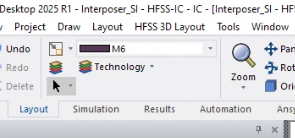

IC 모드 스택업

가장 먼저 확인해야 할 것은 모델의 스택업입니다. 스택업 아이콘을 선택합니다:

IC 모드 스택업은 항상 겹치는 스택업입니다. 이 모드에서는 서로 다른 레이어를 겹칠 수 있습니다. 사용자는 각 레이어의 하부 및 상부 치수를 지정하기만 하면 됩니다. 레이어와 재질을 변경하는 것 외에도 사용자는 에칭 및 표면 거칠기와 같은 효과를 추가할 수 있습니다. IC 모드에는 VIA 레이어도 있습니다. 비아 레이어의 하부 및 상부 치수는 금속 레이어 이름(예: M5, M6 등)을 사용하여 지정합니다.

![]()

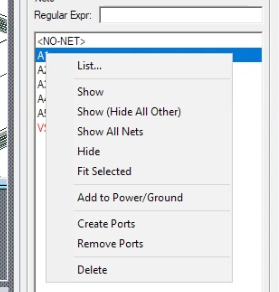

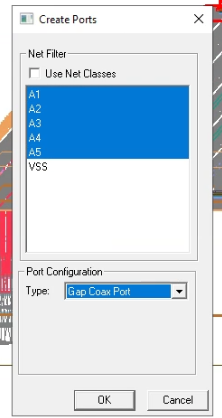

IC 모드 포트

HFSS에서 사용자는 다양한 방법으로 포트를 추가할 수 있습니다. 세 가지 솔버는 모든 유형을 허용합니다. 포트를 추가하는 첫 번째 방법은 네트워크를 선택한 다음 마우스 오른쪽 버튼을 클릭하여 네트워크의 양쪽 끝에 포트를 추가하는 것입니다.

다른 방법은 컴포넌트를 선택한 다음 마우스 오른쪽 버튼을 클릭하여 포트를 추가하는 것입니다:

이 두 가지 방법으로 동축 갭 타입 포트를 생성합니다.

모델 편집

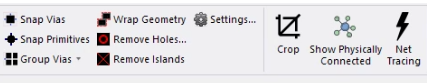

설계 단계, 특히 최적화 단계에서 RaptorX를 사용할 것을 적극 권장합니다. 보다 정확한 결과를 얻으려면 사용자는 HFSS도 활용할 수 있어야 합니다. IC 모드에는 설계를 수정하고 작은 치수를 제거할 수 있는 스마트 도구가 장착되어 있어 HFSS가 지나치게 오랜 시간 동안 실행되는 것을 방지할 수 있습니다.

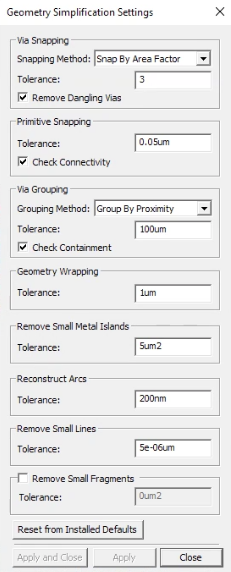

그러나 이러한 기능을 사용하기 전에 사용자는 설정을 수정해야 합니다. 설정 버튼을 클릭합니다:

설정에서 각 숫자의 의미를 이해하기 위해 도구로 돌아가 보겠습니다:

- 비아를 스냅합니다: 이 옵션은 비아의 단면을 상단 또는 하단 레이어의 패드 크기와 일치하도록 변경합니다. 델타가 설정의 비아 스냅 기준에 지정된 것보다 작으면 변경이 이루어집니다.

- 스냅 프리미티브: 이 옵션은 신호 레이어의 네트 모양을 서로 일치하도록 변경합니다. 델타가 설정의 프리미티브 스냅 기준에 지정된 것보다 작으면 변경이 이루어집니다.

- 비아 그룹화: 이 옵션은 비아 간격이 설정의 비아 그룹화 기준에 지정된 것보다 작은 경우 비아를 단일 네트로 그룹화합니다.

- 지오메트리 래핑: 이 옵션은 개체 사이의 간격이 설정의 지오메트리 래핑 기준에 지정된 수보다 작은 경우 네트 또는 비아를 단일 네트/단일 비아로 그룹화하고 간격을 좁힙니다.

- 구멍 제거: 신호 레이어의 네트에 “작은 금속 섬 제거”에 지정된 수보다 작은 단면의 작은 구멍이 있는 경우 해당 구멍을 채웁니다.

- 섬 제거: 이 옵션은 모든 작은 섬을 간단히 삭제합니다. 이 결정은 설정의 작은 금속 섬 제거 기준에 따라 이루어집니다.

세 솔버의 차이점: 결과

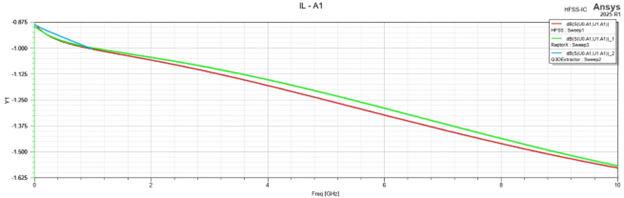

다음 그래프는 세 솔버 간의 차이를 보여줍니다. 최대 1GHz까지 Q3D를 풀었습니다. 이것이 그물의 RLCG를 추출하는 데 필요한 전부입니다.

HFSS와 RaptorX 모두 매우 근접한 결과를 제공했습니다. 이는 사용자가 최적화 과정에서 RaptorX를 신뢰할 수 있음을 나타냅니다. 다음 표는 각 솔버의 풀이 시간을 보여줍니다. 기본 설정을 사용한 HFSS는 RaptorX보다 5배 더 오래 걸렸습니다. 사용자가 모든 오브젝트에서 메시를 제어하여 스마트 메시를 수행하면 이 시간을 개선할 수 있습니다.

| Q3D (C/G/D RL/ AC RL) | RaptorX | HFSS (Q3D를 사용한 DC) | |

| 메모리 | 7G | 12G | 126G |

| 시뮬레이션 시간 | 0:17 | 0:44 | 4:08 |

| 반복 시간 | 0:12 (CG) | 0:57 | |

| 요소 수 | 0.106M 트라이앵글(AC) 0.120M 테트라(DC) | 0.133M | 1.3M 다중 주문 테트라 |

요약

HFSS-IC는 중소기업을 위해 설계된 견고하고 예산 친화적인 솔루션입니다. 이 솔루션은 HFSS와 RaptorX 솔버의 모든 기능을 통합합니다. 이 툴은 다이, 스택형 다이, 패키지상의 다이, PCB에 장착된 복잡한 어셈블리를 포함한 다양한 구성의 설계를 제한 없이 지원합니다. 사용자는 기생 소자 추출, 인덕터 설계, 트랜지션 및 전력 분배기 최적화, 크로스토크 완화 등의 작업을 수행할 수 있습니다.

디자이너를 위한 포럼에 참여하기

여러분의 전문 지식은 커뮤니티에 매우 중요합니다. 참여하여 지식을 공유하세요

지금 포럼에 참여하세요업계 최고의 전문가들과 함께 공유하고 배우며 성장하세요.